Fachartikel vom 01/08/2013

Die Validierung schneller Bussysteme gewinnt heute immer mehr an Bedeutung

Systemlieferanten haben ein wachsames Auge auf die Signalintegrität

Hierbei bietet die Embedded-Instrumentierung mit ihrer Vielseitigkeit, Geschwindigkeit und Präzision eine hohe Bandbreite überzeugender Lösungen zu Sicherstellung der Signalintegrität in elektronischen und mechatronischen Systemen.

|

| (Bild: Asset) |

Selbst die schnellsten und modernsten Prozessoren und Komponenten sind keine Garantie dafür, dass ein System eine hohe Leistung bringt. Wenn der Datenverkehr auf schnellen Chip-to-Chip-, I/O- (Input/Output) und Memory-Bussen wegen mangelhafter Signalintegrität ins Stocken gerät, sinkt der Systemdurchsatz schnell auf ein nicht mehr akzeptables Niveau. Leider ist es ein Irrglaube, dass sich dieses Problem einfach durch Implementierung der schnellstmöglichen Busse lösen lässt. Denn nur allzu oft steht die theoretische Busgeschwindigkeit im direkten Verhältnis zur Komplexität der Aufgabe, dem Bus sein volles Potenzial zu entlocken. Je höher die Busgeschwindigkeit in der Theorie ist, desto schwieriger lässt sich jedoch diese Geschwindigkeit in der Praxis erreichen und halten. Lieferanten von elektronischen und mechatronischen Systemen, die eine optimale Systemperformance anstreben, müssen letztendlich die Validierung der Signalintegrität in jeder Phase des Lebenszyklus in den Griff bekommen – angefangen beim Design, über die Produktion bis hin zum Feldservice.

Augen schließen sich

Über viele Jahre hinweg haben die Ingenieure mit Augendiagrammen gearbeitet, die ihnen eine Momentaufnahme der Signalintegrität auf High-Speed-Bussen lieferten. Aber die höheren Übertragungsgeschwindigkeiten der aufeinander folgenden Generationen moderner Hochgeschwindigkeitsbusse – beispielsweise PCI Express I/II/III, DDR1/2/3 Memory-Bus, Serial ATA I/II/III, USB 1/2/3, Intel Quick Path Interconnect (Intel QPI) und andere – lassen die Augendiagramme zusammenschrumpfen. Das heißt, die Fehlermargen bei der Signalisierung werden immer enger. Das wirkt sich wiederum unmittelbar auf den Busdurchsatz aus, da geringere Betriebstoleranzen automatisch mehr Fehler zur Folge haben, was den Signalverkehr auf dem Bus verlangsamt. Verschärft wird das Problem durch die Eignung – beziehungsweise mangelnde Eignung – der Messinstrumente, die in der Regel zur Erzeugung der Augendiagramme verwendet werden, zum Beispiel Oszilloskope oder die Geräte zum Testen von Leiterplatten in der Produktion wie zum Beispiel ICT-Systeme (In-Circuit-Test).

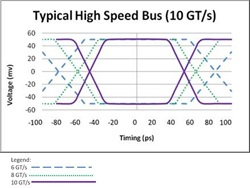

Um das Problem der schrumpfenden Augendiagramme zu verdeutlichen, nehmen wir drei Generationen eines hypothetischen High-Speed-Busses als Beispiel, dessen theoretische Übertragungsgeschwindigkeit von sechs auf acht und schließlich zehn GT/s (Gigatransfer pro Sekunde) steigt. In Bild 1 sind die Augendiagramme für die einzelnen Übertragungsgeschwindigkeiten übereinander gelegt. Mit der Steigerung der Signalfrequenz zur Erreichung einer höheren Transferrate schiebt sich das Augendiagramm immer mehr zusammen, was zeigt, dass die Betriebstoleranzen für Spannung und Timing immer enger werden. Ein geringerer Fehlerspielerraum bedeutet, dass ein geringeres Maß an Jitter, Dämpfungen der Signalspannungspegel und Abweichungen im Fertigungsprozess ausreicht, um die Busperformance zu beeinträchtigen. Mit anderen Worten: Weniger oder kleinere Anomalien können größere Signalverzerrungen verursachen, die sich negativ auf die Busperformance auswirken.

|

| Das Augendiagramm schrumpft mit jeder neuen Highspeed-Bus-Generation (Bild: Asset) |

Ein genauerer Blick auf die Timingprobleme verdeutlicht diesen Punkt. Bei sechs GT/s hatte die erste Generation dieses Busses ein relativ breites Augendiagramm entlang der Zeitachse (X-Achse). Das Auge misst hier eine Breite von cirka 166 Picosekunden (ps). Bei der nächsten Generation des Busses, die mit einer höheren Frequenz arbeitet, um eine Übertragungsgeschwindigkeit von acht GT/s zu erreichen, ist die Breite des Auges auf 125 ps geschrumpft, wodurch die Betriebstoleranzen um 25 Prozent reduziert wurden. Bei der dritten Generation des Busses wurde die Signalfrequenz weiter gesteigert, um eine Übertragungsgeschwindigkeit von 10 GT/s zu erreichen. Bei dieser Geschwindigkeit schrumpft die Breite des Augendiagramms noch einmal auf rund 100 ps, was einer Reduzierung um zusätzliche 20 Prozent entspricht. Diese zwei Verkleinerungen der Augenbreiten mögen für sich genommen zwar eher graduell wirken, aber die Gesamtreduzierung der Betriebstoleranzen über die drei Generationen der Bustechnologie – wahrscheinlich im Laufe von zwei bis fünf Jahren – hinweg, summiert sich auf signifikante 40 Prozent, also einer Verringerung der Betriebstoleranzwerte um knapp die Hälfte.

Neben Timing-Anomalien können auch andere Faktoren die Signalintegrität beinträchtigen, beispielsweise Jitter beziehungsweise Leitungsrauschen sowie die Dämpfung der Signalpegel zwischen Sendern und Empfängern oder Abweichungen im Fertigungsprozess sowohl auf Chip- als auch auf Leiterplattenebene. Zudem haben Onboard-Schwankungen bei der Spannungsregelung und bei den Betriebstemperaturen auf Systemebene unter Umständen starken Einfluss auf die Signalintegrität.

Kann man dem Oszilloskop trauen?

Aufgrund der Tatsache, dass die Systemlieferanten heute die Signalintegrität auf High-speed-Bussen genauer im Auge haben, werden die Grenzen der Messinstrumente deutlich, mit denen die Signalintegrität traditionell gemessen wird, nämlich Oszilloskop und Logikanalysator. Genau der Faktor, der die Signalintegrität zum kritischen Punkt gemacht hat, nämlich die ständig steigende Nachfrage nach höherem Systemdurchsatz, verursacht die Probleme bei Messungen mit sondenbasierten beziehungsweise mit Tastköpfen arbeitenden Messgeräten: Oszilloskope in der Designphase und bei Feldservicearbeiten, ICT-Systeme, Flying Probe Tester und Manufacturing Defect Analyzer in der Fertigung.

Die Schwierigkeiten sind auf die kapazitativen Kopplungseffekte zurückzuführen, die die Sonden (Tastköpfe) auf die äußerst empfindlichen High-speed-Busse mit ihren immer engeren Betriebstoleranzen haben. Bereits das Anlegen eines Tastkopfs am Bus bewirkt Verzerrungen des Signals. Auch das Anbringen eines Testpunkts an einem Bus für den Sondenzugang führt zu Anomalien. Deshalb sind Testpunkte an diesen hoch sensitiven Bussen in den Best-Design-Practices heute in der Regel nicht mehr vorgesehen. Somit ist die Validierung mit einem sondenbasierten Instrument nicht mehr möglich. Selbst wenn der Zugangspunkt verfügbar ist, lässt sich die Signalintegrität nur mit teuren High-end-Oszilloskopen messen, da diese Oszilloskope in der Lage sein müssen, mit komplexen mathematischen Modellen das unverfälschte Signal aus dem beobachteten Signal herauszurechnen beziehungsweise herauszufiltern, denn das vom Oszilloskop erfasste Signal beinhaltet auch die Verzerrungen, die der Tastkopf selbst erzeugt hat.

Glücklicherweise gibt es eine wirtschaftlichere und einfachere Methode zur Gewinnung von empirischen Daten der Signalintegrität. Heutzutage werden die verschiedensten Validierungs-, Test- und Debugging-Instrumente in die Halbleiter eingebettet. Einige können die Integrität der Bussignale erfassen und auch andere Testfunktionen ausführen. Auf diese eingebettete Messinstrumentierung wird normalerweise über Standardtechnologien zugegriffen, beispielsweise über den IEEE 1149.1 Boundary-Scan (JTAG) Test Access Port (TAP), der in praktisch allen Prozessoren und vielen anderen Bausteintypen zu finden ist. JTAG ermöglicht den Zugriff auf eine externe softwarebasierte Plattform, die die im System eingebetteten Instrumente verwalten und deren Test- und Messergebnisse auslesen und auswerten kann.

Validierung über den gesamten Lebenszyklus

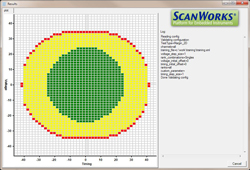

|

| Das Augendiagramm in dieser Bildschirmdarstellung wurde mit einer Instrumentierung erzeugt, die im Chip eingebettet ist. (Bild: Asset) |

Aufgrund der kritischen Bedeutung der Busperformance und ihrer Auswirkung auf den Systemdurchsatz entwickelt sich die Validierung der Signalintegrität von High-speed-Bussen in allen Phasen des Systemlebenszyklus immer stärker zu einer Notwendigkeit. Aber in jeder Phase des Lebenszyklus werden verschiedene Typen von Validierungstests implementiert. Zwar bestimmen die Anforderungen der jeweiligen Phase die Art der verwendeten Validierungsroutinen, aber für sämtliche Validierungsvarianten avanciert die kontaktlose eingebettete Messinstrumentierung rasch zum gemeinsamen Nenner.

In der Designphase muss nach der Assemblierung der ersten Prototypen einer Leiterplatte beispielsweise die Busperformance validiert werden, um sicherzustellen, dass das Design die Performance-Spezifikationen des Pflichtenhefts erfüllt. Es müssen Tests aus vielen unterschiedlichen Perspektiven durchgeführt und erhebliche Datenmengen erfasst werden, um zu gewährleisten, dass die Leistung des Prototyps den Designvorgaben entspricht, bevor er für die Produktion freigegeben wird. Im Gegensatz zu Funktionstestmethoden ist die Embedded-Instrumentierung in der Lage, die High-Speed-Busse eines Systems noch vor der Integration von Firmware oder eines Betriebssystems zu validieren. Auf diese Weise kann die Softwareentwicklung unabhängig von diesem Board-Bring-up-Prozess fortgeführt werden.

In der Fertigung ist die Validierung der Busse notwendig, um zu gewährleisten, dass Abweichungen im Produktionsprozess keine Verschlechterungen der Busperformance verursacht haben. Da die Testzeiten kurz sein müssen, um die Fertigungslinie nicht aus dem Takt zu bringen, reicht ein Vierpunkt-Toleranztest zur Prüfung, um festzustellen, dass die Busse effektiv und mit maximaler Geschwindigkeit laufen. Bei Systemen im Feld ist die Validierung letzen Endes ein entscheidendes Diagnosetool, um die Ursachen für einen mangelhaften Systemdurchsatz zu identifizieren. An diesem Punkt im Lebenszyklus ist die Testdauer nicht so kritisch wie die Feststellung der Ursachen von Störungen und Fehlern und die Ermittlung einer effektiven Methode der Fehlerbehebung.

Autor:

Tim Caffee ist Vice President of Design Validation and Test bei ASSET InterTech