Fachartikel vom 02/05/2013

Effizienz steigern, Qualität verbessern, Sicherheitsnormen erfüllen

Motoren sparsam und effizient regeln

Flexibilität erweitern, schnell und effektiv Entwickeln sind die Attribute der heutigen modernen Antriebstechnikentwicklung. Dazu kommt auch ein enormer Druck der Kostensenkung auf die Entwicklungsingenieure. Dieser Artikel zeigt, dass auch 16-bit Steuereinheiten in den 32-bit Bereich eindringen sowie die erwähnten Attribute beibehalten können.

Der bürstenlose Dreiphasen-Motor (BLDC) oder der Permanentmagnet-AC-Motor (PMAC) sind Typen von Motoren, die in den verschiedensten Applikationen der modernen Antriebstechnik vermehrt Einsatz finden. Dies geschieht aufgrund ihrer Wirkungsweise sowie der dazugehörigen Leistungseffizienz im Bereich Drehmoment, Drehzahlerzeugung, Dynamik und langer Lebensdauer. Zusätzlich zu den typischen Merkmalen der Ansteuerung dieser Motoren kommen nicht nur die zunehmende Komplexität und weiter wachsende Ansprüche an ebendiese sondern auch höhere Anforderungen an die Systemqualität zum Tragen. Gilt das Interesse insbesondere der Zuverlässigkeit, erhöhter Sicherheit und der Flexibilität bei der Entstehung einer Plattformlösung, dann ist die Vorgehensweise eines Entwicklungsingenieurs ziemlich eng vorgegeben. Dabei ist das Attribut der hoch sensitiven kostenoptimierten Entwicklung maßgebend. Die auf diese Weise zu entwickelnden Systeme fordern Steuereinheiten, die Flexibilität bei der Gestaltung des Systems garantieren. Dabei spielt der Faktor der Kostensenkung aufgrund des Verzichts der externen Bauteile eine sehr wichtige Rolle bei der Auswahl des geeigneten Produktes.

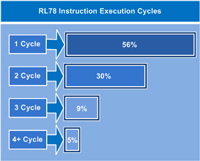

Mit der 16-bit RL78-Familie aus dem Hause Renesas Electronics wird eine Linie an Steuereinheiten angeboten, die sich sehr gut den verschiedensten Anforderungen der Applikationen auf dem Markt anpasst. Diese bietet innerhalb der Familie eine sehr hohe Flexibilität bei der Wahl des geeigneten Mikrocontrollers sowie folgende Charakteristiken: flexible Timer-Peripherien mit vielfachen Funktionsmöglichkeiten, optimierte und flexible Signalerzeugung, intern programmierbare Hardware-Verbindungen für schnellere System-Zustandsabarbeitungen sowieeine programmierbare Intelligenz, um sparsamste Stromverbrauchsmodi zu ermöglichen. Im Bereich der speziellen industriellen Segmente wie der Antriebstechnik ist der G14 als Mitglied der RL78-Familie ein 16-Bit-Derivat, das sich sehr gut zur Ansteuerung von verschiedenen Typen von Motoren eignet. Die Grundarchitektur der RL78-Familie als Mix zwischen der 78K0R- und R8C-Familie liefert ein Ergebnis von 1,27 DMIPS/MHz. Dabei ist die Stromaufnahme mit 70 µA/MHz bei maximaler Taktfrequenz von 32 MHz zu kennzeichnen. Die Ausführung einer Instruktion kann zwischen 0,03125 µs bei 32 MHz internen High-Speed-Clock bis hin zu 30,5 µs bei 32,768 KHz Taktung mit dem Subsystemtakt eingestellt werden. Der Instruktionssatz bietet eine Vielfalt an Befehlen, von denen 56 Prozent der insgesamt 87 Instruktionen innerhalb eines Taktes ausgeführt werden können. Die restliche Aufteilung der Ausführungen kann Bild 1 entnommen werden.

|

| Bild 1: Aufteilung der Instruktionen mit deren Ausführungstakten (Bild: Renesas) |

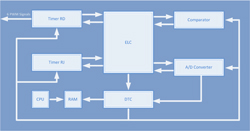

Die CISC-Harvard-Architektur enthält eine dreistufige Pipeline, 8 Bit x 8 Register x 4 Bänke und einen 16-Bit-Barrel-Shifter. Die DSP-Funktionen, wie die 16 x 16 vorzeichenlose und -behaftete Multiplikation, die 32/32-Division sowie die sogenannte MAC-Instruktion (Multiply and Accumulate) bieten eine enorme Flexibilität und Rechenleistung. Diese beweist sich als sehr nützlich bei der Ausführung von komplexen Algorithmen, die intensive Rechenoperationen ausführen müssen. Die MAC-Instruktion kann innerhalb von zwei Takten eine 16 x 16-Bit-Multiplikation und dazu eine 32-Bit-Addition ausführen und ist sehr gut geeignet für Filterberechnungen. Hinzu kommen eine Vielfalt an flexiblen Peripherien, wie das DTC-Modul (Data Transfer Controller) und der Event-Link-Controller (ELC), welche zur Entlastung der CPU beitragen. Sie bieten die Möglichkeit, eine in Hardware verbundene Schleife aufzubauen, die in Echtzeit auf externe Events reagieren kann, ohne die notwendigen Standardwege durch die CPU gehen zu müssen. Bild 2 zeigt das gesamte System des Derivats G14 mit allen entsprechenden Charakteristiken, die diesen Baustein auszeichnen. Die Aufteilung der angebotenen Derivate aus der G14-Serie fängt bei der kleinsten Version als 30-Pin-Version mit 16 KByte Flash, 2,5 KByte RAM und 4 KByte Datenflash an und geht bis zu dem größten 100-Pin-Derivat mit 96 KByte Flash, 12 KByte RAM und 8 KByte Datenflash. Zu dem Programmflash kommt noch das Datenflash mit einer Größe von 4 KByte oder 8 KByte abhängig von der Größe des G14-Derivats hinzu. Das Datenflash kann im Hintergrund parallel zur Applikationssoftware betrieben werden und so wichtige Systemparameter speichern und als EEPROM-Ersatz dienen. Der High-Speed-Oszillatortakt kann zwischen 64 MHz, 32 MHz, 24 MHz bis hin zu 1 MHz eingestellt werden und ist mit einer Genauigkeit von ± 1 Prozent behaftet und zwar über den gesamten Spannungs- und Temperaturbereich. Hierbei ist zu bemerken, dass der maximale interne Takt von 64 MHz nur dem 16-bit Timer RD zur Verfügung steht.

|

| Bild 2: System Aufbau des RL78/G14 Derivats (Bild: Renesas) |

Die CPU und der Rest der Peripherien begnügen sich im High-Speed-Bereich mit dem maximalen Takt von 32 MHz. Die RL78-Familie bietet zudem einige spezielle Hardware-Sicherheitsfunktionen. Diese ermöglichen eine ideale Unterstützung bei der Realisierung und Einhaltung des Sicherheitsstandards IEC60730 und führen noch zur Entlastung der CPU-Last beim Testen. Funktionen, die softwaremäßig nicht ausgeführt werden können, wie RAM-Write-Protection oder SFR-Write-Protection, sind auch zu den anderen vorhandenen Funktionen implementiert. Im Bezug auf den Einsatz der Ansteuerung und Regelung eines BLDC- beziehungsweise PMAC-Motors, liegt das besondere Interesse bei der Betrachtung des G14-Innenaufbaus an den Peripherien wie dem Dreiphasen-Timer RD, dem A/D-Wandler und den schon erwähnten Peripherien wie DTC und ELC. Diese werden im Folgenden näher erläutert.

Eigenschaften des Analog-Digital-Wandlers

Im analogen Bereich der G14-Serie ist der Analog/Digital-Wandler (ADC) mit einer Wandlungsauflösung von 10 Bit und einer minimalen Wandlungszeit von 2,1 µs zu finden. Die A/C-Wandlung kann zusätzlich zur Software auch durch andere interne Peripherien angestoßen werden. Einer der möglichen Quellen des Startsignals kann auch eines der Timer-Module sein, die in Kombination mit dem ELC-Modul eingesetzt werden können. Der Spannungsbereich, in der die Wandlungen stattfinden können, beträgt 1,6 V bis 5,5 V. Das ADC-Modul beinhaltet eine interne Referenz-Spannung von 1,44 V, die entweder als Referenz- oder als Eingangsspannung benutzt werden kann. Zusätzlich ist noch der interne Temperatursensor in dem Modul zu finden, der den gemessenen Wert an einem der ADC-Ergebnisregister schon digital zur Verfügung stellt.

Eigenschaften des DTC-Moduls (Data Transfer Control)

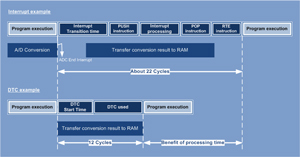

Das DTC-Modul ermöglicht Daten-Transfers innerhalb des Speichers ohne dabei die CPU zu belasten. Dafür stehen bis zu 24 Kanäle zur Verfügung. Der Transfer wird mittels eines Interrupts einer Peripherie angestoßen. Dabei wird die Quell- und Ziel-Adresse benutzt, um die Daten von und an die entsprechenden Stellen zu transferieren. Der eingestellte Modus sowie die Quell- und Zieladresse des Transfers sind im Control-Bereich des DTC-Moduls gespeichert. Dieser Control-Bereich ist im RAM-Speicher allokiert und wird durch das DTCBAR-Register definiert. Es gibt insgesamt bis zu 31 Quellen zur Aktivierung des DTC-Transfers und diese können in ihrer Priorisierung eingestellt werden. Die maximale Datengröße, die transferiert werden kann, beträgt 512 Byte bei einem 16-bit-Datentransfer. Dabei unterscheidet sich die Art des Transfers zwischen Normal- und Repeat-Modus. Im Normalmodus wird die Aktivität des DTC-Moduls nach einem einzelnen Transfer der entsprechenden Daten beendet. Beim Repeat-Modus hingegen wird der Transfer der Daten weiter durchgeführt in dem die Zieladresse automatisch initialisiert und der Register-Wert noch einmal geladen wird. Hierbei ist die Menge der Daten, die transferiert werden sollen, einstellbar. Die Beendigung des Datentransfers durch das DTC-Modul wird mit einem Interrupt quittiert: erstens nach jedem Transfer im Normalmodus und zweitens nach dem gesamten Transfer der eingestellten Datenmenge im Repeat-Modus. Im Standby-Modus, wie HALT oder SNOOZE, ist das DTC-Modul funktionsfähig und einsetzbar. Dadurch ist die Funktion des Datentransfers im Strom sparenden Systemzustand gewährleistet und kann zum Aufwachen der CPU in den aktiven Zustand genutzt werden. Bild 3 zeigt ein Beispiel des Datentransfers vom A/D-Wandler zum RAM und stellt die Vorteile der DTC-Benutzung gegenüber der Standard-Vorgehensweise über einen Interrupt dar.

|

| Bild 3: Beispieldarstellung der Vorteile einer DTC-Benutzung gegenüber der Standard-Interrupt-Vorgehensweise (Bild: Renesas) |

Die Eigenschaften des ELC-Moduls

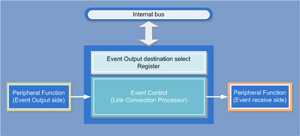

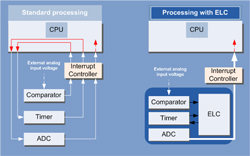

Das ELC-Modul (Event Link Control) ermöglicht programmierbare Verbindungen zwischen den Ausgangsevents der verschiedensten Peripheriefunktionen. Das Block-Diagramm des ELC-Moduls ist aus Bild 3 zu entnehmen. Durch diese internen Peripherie-Verbindungen ist eine Koordination zwischen den Peripheriefunktionen möglich, ohne die notwendigen Standardwege durch die CPU eingehen zu müssen. Dadurch kann die Interrupt-Abarbeitung drastisch reduziert und die Größe der Software optimiert werden. Durch die reduzierte Interrupt-Abarbeitung - wie in Bild 5 dargestellt - und die direkte Kontrolle über I/O-Ports, wird das Echtzeitverhalten des Systems verbessert. Das ELC-Modul kann von 20 bis hin zu 26 Typen an Eventsignalen zwischen den Peripherien verbinden (Linken).

Die Eigenschaften des 16-bit Timer-Moduls RD

|

| Bild 4: Das Blockdiagramm des ELC-Moduls (Bild: Renesas) |

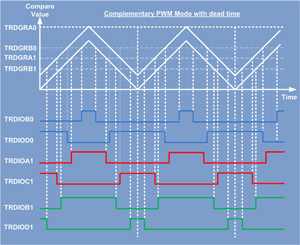

Das RD-Timer-Modul beinhaltet 2 x 16-Bit-Timer RD0 und RD1 mit jeweils vier I/O Pins. Zu den Standard-Funktionen, wie die Input-Capture- oder die Output-Compare-Funktion, hat dieses Modul noch drei einstellbare PWM-Modi wie folgt: Reset-Synchronous-PWM-Mode, Complementary-PWM-Mode und PWM3-Mode. Der zweite Modus generiert sechs mittenzentriert gewichtete Dreiecks-Phasen-Signale. Diese werden automatisch mit einer vordefinierten Totzeit beaufschlagt. Der Signalverlauf dieser komplementären Dreiphasen-PWM ist in Bild 7 dargestellt. Alle drei Modi benötigen jedoch die Kombination der beiden Timer. Die Pin-Zuordnung der Timer-Ausgänge ist abhängig von der ausgewählten Funktion des Timers.

|

| Bild 5: Gegenüberstellung des ELC-Moduls zur Standard-Verfahrensweise (Bild: Renesas) |

Das Timer-RD-Modul ist mit einem Shut-Off-Mechanismus ausgestattet, der die Ausgänge des Moduls deaktivieren und in einen definierten Hi-Z-Zustand schalten kann. Hierdurch kann das System bei Überströmen automatisch ausgeschaltet werden. Dieser Sicherheitsmechanismus hat zusätzlich noch die Möglichkeit, durch das erwähnte ELC-Modul angesteuert zu werden. Hierdurch kann das Abschalten der Ausgänge auch durch andere auftretende Events ausgeführt werden. Ein Beispiel dafür wäre die Benutzung des implementierten Komparators. Dieser besitzt zwei Kanäle und kann mit der sogenannten Window-Funktion zur Spannungsüberwachung eingesetzt werden. Dies gewährleistet, dass der Leistungsteil des Systems (zum Beispiel Wechselbrücke) immer vor Überstrom oder Spannungseinbruch geschützt bleibt.

Kombination der Module im Bereich der Antriebstechnik

|

| Bild 6: Timer RD Block-Diagramm (Bild: Renesas) |

Durch die Kombination der erwähnten Module miteinander ist ein eigenständiger Mechanismus möglich, der auf der Hardwareebene automatisch die Steuerungsabläufe übernehmen kann. Dabei wird die CPU für die Koordination nicht mehr gebraucht und somit entlastet. Stattdessen kann die CPU-Zeit für die Abarbeitung der mathematischen Berechnungen oder Auswertung der Kommunikation genutzt werden. Wie eine mögliche Kombination dieser Module aussehen könnte, zeigt Bild 7. Der Timer-RD generiert die notwendigen Dreiphasen-PWM-Signale für die Ansteuerung des BLDC- oder des PMSM-Motors. Der Datentransfer der Systemvariablen kann in einer automatisierten Hardwareschleife stattfinden. Dadurch wird die Echtzeitverarbeitung verbessert und führt zu einer Optimierung der Regelungsgüte und Regelungsdynamik des Systems. Die Automatisierung des Datentransfers erfolgt durch die Hardwareverbindungen der Peripherien mit dem ELC- und DTC-Modul. Mit dem Funktionsstart des RD-Timers wird durch das ELC-Modul auch der Timer RJ gestartet und zwar als Intervall-Timer. Dieser generiert die einstellbaren Trigger-Zeitpunkte für den A/D-Wandler. Damit kann die Messwerterfassung des Stromes, der BEMF und der Spannung mit der PWM innerhalb einer Periode synchronisiert werden.

|

| Bild 7: Mögliche Modul-Kombination und deren automatisierte Verbindung (Bild: Renesas) |

Dies ermöglicht die Messung mit wenig oder gar keiner Beeinflussung durch Störsignale. Das führt zu Reduktion oder Verzicht des Einsatzes von externen Filterschaltungen und interner Softwarefilterberechnungen. Die CPU kann somit von diesen externen Datenerfassungen, Transfers und Eventabarbeitungen entlastet und für die Abarbeitung der Regelungsberechnungen und Auswertung der zur Verfügung stehenden Daten eingesetzt werden. Wie so ein aufgestelltes System effektiv und sparsam funktioniert, zeigt das von Renesas Electronics entwickelte Demo-System. Das Demo-Kit bietet die Variante einer sensorlosen Drei- oder Ein-Shunt-Feld-Orientierten-Regelung (FOC) eines PMSM-Motors. Hierzu ist eine Open-Source-Softwarebibliothek mit allen notwendigen Softwarefunktionen für die Ansteuerung und Regelung vorhanden. Zusätzlich zur gesamten Dokumentation und zum Layout des Hardware-Boards wird auch eine GUI-Software angeboten. Diese gibt dem Entwickler die Möglichkeit, alle wichtigen Systemparameter selbst einzustellen und somit bei der Evaluierungsphase zu optimieren. Dadurch ist der Einsatz mit dem kundenspezifischen Motor für die Applikation gegeben und ein schnelles Vorantreiben einer effektiven und kostenoptimierten Entwicklung gewährleistet.

Autor

Suad Jusuf ist bei Renesas beschäftigt